# GN-0483-2 VME TRACK FINDER PWB

VME トラック ファインダー プリント配線基板

### 概説

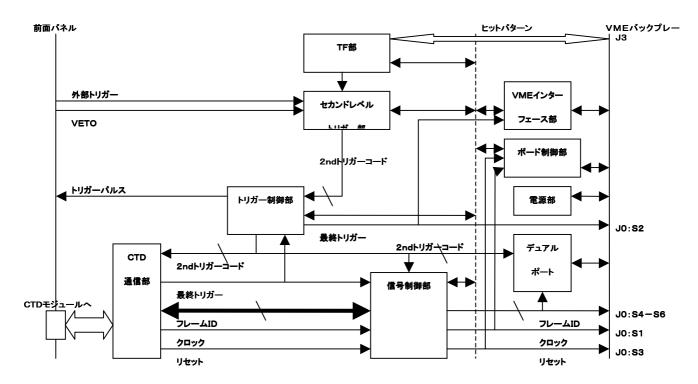

このプリント配線基板は、テレスコープアレイ実験用に開発されたものです。現在一般的に使用されている VME 規格と同じサイズ、ユーロカード トリプル ハイト(90)の 配線基板です。トラックファインダーは TF部、セカンドレベルトリガー部、トリガー制御部、信号制御部、CTD部、VMEインターフェース部、ボード制御部、電源部から構成されており。データの流れは以下のとおりです。

16枚のSFモジュールから各々16チャンネル分のトリガーパターンとトリガーコード(0/1/2/3)が集められ、TFモジュールでメモリールックアップ方式による、トラック判定が行われ。その結果、セカンドレベルトリガー部がセカンドレベルトリガーコードを生成してトリガー制御部に送ります。トリガー制御部は外部バスを通じてトリガーコードをCTDモジュールに送り、結果としてトリガー信号を受け取ります。トリガー制御部はトリガーを受けるとVMEバックプレーンを通じてすべてのSDFモジュールにトリガーを送るとともに、データ収集開始のための割り込み信号をPCに送る機能があります

## 仕樣

トラックファインダー(TF)部 セカンドレベルトリガー部 トリガー制御部 信号制御部 CTD通信部

電源部 使用電源 + 5 V、 + 3 . 3 V、 - 5 V、 - 3 . 3 V 1 W 9 U VME モジュール JO 有り ( KEK VME 規格)

#### TFモジュール ブロック図

#### 各種装置との接続機能

外部機器 (デバッグ用)

(受信) VETO: NIM, レベル

(受信)外部トリガー:NIM、エッジ

(送信)トリガー出力:NIM、エッジ

SDFモジュール

(送信)システムクロック: L V D S、エッジ、 J 0: S 1

(送信)最終トリガー: LVDS、エッジ」0: S2

(送信)リセット: L V D S、エッジ、 J 0: S 3

(送信)フレームID(下位3ビット): LVDS、レベル、J0:S4-S6

(受信)ヒットパターン:17ビット、LVDS、J3

1ビット×16ch+non conditional

シリアライザ/でシリアライザ DS 9 2 LV1023 / 1224 を使用してクロック + データを同時に送る。

(バスの本数が減らすため。しかし TF 側でデコード回路が必要)

CTDモジュール

シリアライザ DS 9 2 LV1023 / 1224 を使用してクロック + データを同時に送る。コネクタは RJ45 とする。 L V D S ではあまり長い ( $>30\,\mathrm{m}$ ) のケーブルを使用すると誤動作する可能性があります。テストの必要あり。

(受信)システムクロック:40~66MHz、エッジ

(送信)2ndレベルトリガーコード:3ビット(1-3)

(送受信)フレームID:16ビット(?)

(受信)最終トリガー:1ビット、エッジ

(受信)リセット:1ビット、エッジ

PCI-VMEインターフェース

割り込み、データ送受信、コマンド、ステータス、FPGAなどの書き換え、それらのためのハンドシェイク