# GN-1196-2(A,B) SA03 TEST BOARD SYSTEM

SA03 テスト基板 システム

#### 概説

本テスト システムは 高エネルギー加速器研究機構で行われる Aerogel - RICH 実験に 使用される集積回路 の事前検査用システムとして開発されました。本システムは メイン基 板A サブ基板Bより 構成されております。同時に複数のSAO3 の性能評価を行うことができ 作業時間短縮ができます。

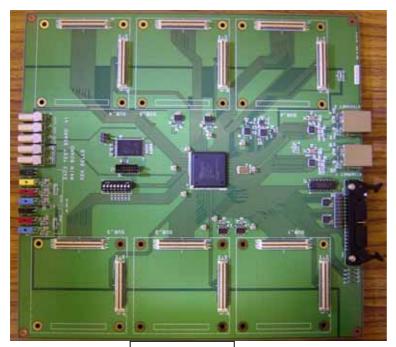

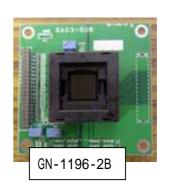

メインボードにFPGAなどの素子や電源を設置し、サブボードにLTCCパッケージのSA03を配置することができるソケットを配置しました。 下記にその写真を示します。

大きい基板を SA03 TESTメイン基板 GN-1196-2(A)

計測集積回路を入れる 基板を SA03 TESTサプ基板 GN-1196-2(B) としました

GN-1196-2A

### 特徵

メインボードの上にスタンド型のコネクタが配置されており,この上にサブボードを接続し,サブボードに設置したSAO3 と通信を行う。メインボードとサブボードを分けた理由はFPGA が故障した場合,ソケットが全て無駄になることを防ぐためである。また,ソケットのみ破損した場合も取り替えサブボードを変えることによって6 つのSAO3 を測定することができる。最大サブボードは6 個接続することができるため,最大 6 個の SAO3 をテストすることが可能である。

## 仕様

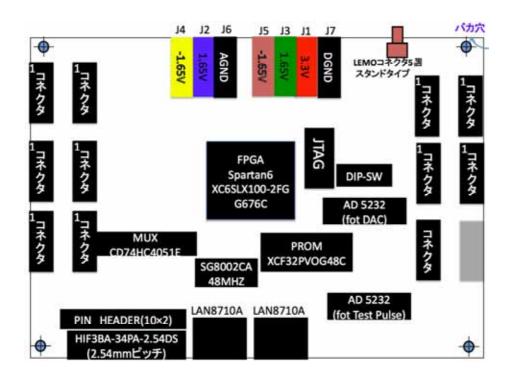

本ボードに搭載したFPGA はXilinx 社製のSpartan6 を使用しており,それぞれパッケージはFG(G)676,デバイスはXC6SLX100 を使用した。また,ROMには本FPGA に対応しているXCF32PVOG48C を採用した。このROMによってFPGA に設定したパラメータの保存が可能である。

FPGAのピン数から最大6 個まで接続可能であったため,6 個のサブボードと繋げることができるようになっている。また,測定はこれまでのSA02,SA03 の性能評価のようにThreshold scan によって行うため,DAC の機能が必要である。そのため,ポテンショメータのAD5232 を採用した。AD5232 は8 bit で制御できるため256 段階の閾値電圧の設定が可能である。また,SA03 に入力するテストパルスを生成するために,AD5232 をもう1 つ設置した。これにより0"3.3 Vの間の大きさのテストパルスを生成することができる。また,本ボードにはアナログ信号をモニターするために3 bit のマルチプレクサCD74HC4051E を設置した。これにより6 つのSA03 からどの信号をモニターするか選択することができる。なお,DIP-SW はSiTCP 通信のアドレス設定のために,AT93C46D はSiTCP 通信用のROMに使用する。Ethernetケーブルのコネクタには一般的に使用されているLAN8710 を採用した。下に各機能素子の配置図を記す

#### 基板什樣

共通事項 基板素材 FR-4 6層 T=1.6mm

サブ基板サイズ:7cmx7cm

メイン基板サイズ: 24.5cm x 25.5cm